TPA-11/56x számítógép

A TPA-11 számítógépcsalád sikereit és tanulságait kihasználva, a ’80-es évtized során a KFKI Mérés és Számítástechnikai Kutató Intézetében (KFKI MSZKI) két vonalon kezdtek fejleszteni LSI technológián alapuló 16 és 32 bites számítógépeket, amelyeket a nagy sebességű, 32 bites szinkron sínrendszer (Xbus) rokonít.

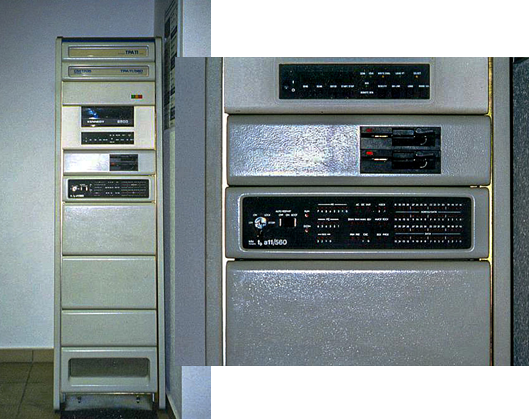

A 32 bites vonalon a DEC VAX (Virtual Address eXtension) architektúrával – emuláció révén – kompatibilis, TPA-11/56x (x∈{1,…,4}) többprocesszoros számítógép kifejlesztése volt a cél. ( Baloldali kép: 561 gép, jobboldali kép: 562 géprészlet).

Saját fejlesztésű (1987-1990), a DEC VAX architektúrával emuláció révén kompatibilis, több (legfeljebb 4) processzoros számítógép kifejlesztése

Főtár: Kertes Róza (MMX)

Lebegőpontos számolómű: Forró Tibor

Sínrendszerek: Xbus: Lőrincze Géza, Tomsics László; - ubus: Briglevics Miklós

Használat

- Lokátor vezérlés (TKI)

- Távközlési Kutató Intézet (TKI)

- INEUM Intézet (Moszkva)

Felépítés

Központi egység

Szószervezésű gép: 32 bpW

- vezérmű (CPU): AM 2900 32/4 bites (D-PAL = Programmable Array Logic) bitszeletes technológiára épülő, mikroprogramozott (legfeljebb 4) processzor

- 32 bites (Xbus) és 16 bites (unibus) sínrendszer

- RAM mikroprogramtár, ciklusidő 100 ns,

- a bitszeleteken egy mikroprogram-lépés ideje: D =10 ns

- főtár: 16 MB DRAM (MMX = Main Memory and Xbus)

- 2×64 KB asszociatív szervezésű gyorsító tár (cache)

- virtuális címfordító (512 lapos Translation Buffer),

- számolómű:

- 32/4 bit-es bitszelet alapú fixpontos számolómű

- nagy integráltságú lebegőpontos számlómű

- Csatorna (CBX= Cache és Xbus csatoló):

- Xbus:

- 64 bit/2×50 ns osztott olvasási ciklus

- 32 bit/50 ns írás ciklus

- 16 címzett egyidejű fogadása

- unibus adapter (UAX = Unibus Adapter and Xbus): szabványos külső eszközök kiszolgálása

- Xbus:

Periféria

- közös konzol az összes processzorra:

- mikroprogram betöltés hajlékonylemezről

- központi processzorok indítása/leállítása

- mikrodiagnosztika önálló mikrokóddal

- natív utasításkészletű tesztek futtatása

- operációs rendszer (VAX VMS) betöltése/indítása

Működés

A számítógép – emulációval – megvalósítja a DEC VAX 11/730 (Virtual Address eXtension) számítógép működését, master/slave módban

Teljesítménye 1 VUP/s (VAX Unit of Performance) processzoronként, ami 3-szorosa az emulált számítógépének

Programkészlet

- operációs rendszer: VAX VMS

Teljes VAX-11 utasításkészlet megvalósítása

Történeti érdekességek

A VAX-11 utasításkészletet megvalósító mikroprogram forrásnyelvi szinten kompatibilis maradt az emulált számítógépével.

A sebességnövekedés jelentős részét az új hardver lehetőségekhez optimalizált és módosított, saját mikrokód eredményezte.

A katonai igényekhez igazítva készült egy military kivitel is (szélsőséges hőmérséklet és rázásállóság, stb.); ezen a mikrokód és a mikrodiagnosztika betöltése – a katonai környezeti feltételekhez igazítva – EEPROM hajlékonylemez-emulációval valósult meg.

Létrehozva: 2021.07.24. 20:10

Utolsó módosítás: 2025.02.25. 14:34